Answer: Option C.

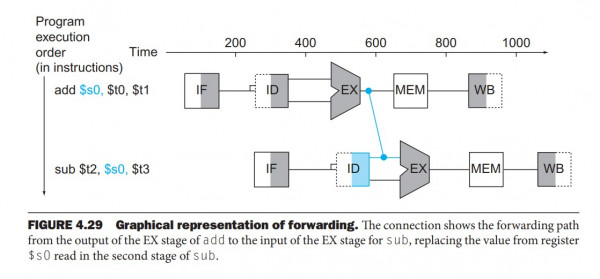

Each Option is discussed in THIS lecture on "Forwarding in pipeline".

Option A: False.

Correct statement is: In a pipelined execution, forwarding means the result from a destination stage of an earlier instruction is passed on to the source stage of a later instruction. See HERE.

Option B: False, because of "next instruction".

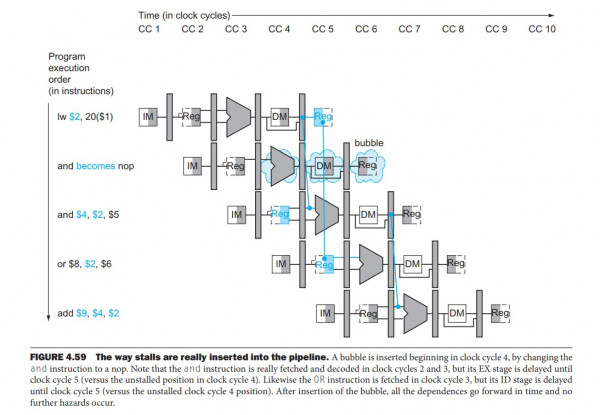

1. In forwarding, data from the output of the MEM stage can be passed on to the input of the EX stage of the next instruction. FALSE.

2. In forwarding, data from the output of the MEM stage can be passed on to the input of the EX stage of a later instruction. TRUE.

3. In forwarding, data from the output of the MEM stage can be passed on to the input of the EX stage of the next instruction, after a stall. TRUE.

In the graphical representation of events (timing diagram that we draw for execution), forwarding paths are valid only if the destination stage is later in time than the source stage. For example, there cannot be a valid forwarding path from the output of the memory access stage in the first instruction to the input of the execution stage of the following, since that would mean going backward in time (tine travel).

Option B is False & Option C is True. Explained HERE.

Option D: False. We need to create forwarding datapaths. Explained HERE.

Image Source: COA book by Patterson.