I know this question is already asked,

But here my doubt is different, I have seen many people calculating the RAW hazard without seeing the no of stages in the pipeline which is not correct.

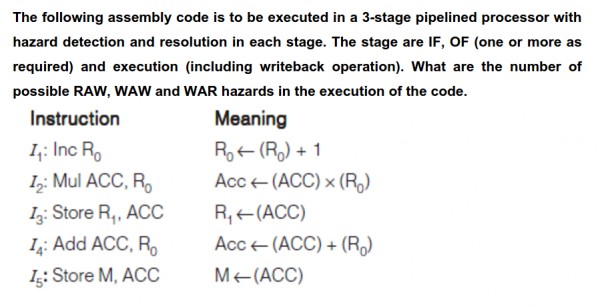

In the above question If we see clearly by keeping in the mind that no of stages given are 3,

From the above question, Inst I1 modifying the data item r0 it will successfully writes the data item r0 at the end of 3rd clock cycle, so the main point is that whatever be the next instruction coming after the EX(which includes WB also) stage that will not have RAW dependency because till that time r0 is written onto the register file, and thus the instruction will read the correct value and this should not included in the RAW hazard but in the solution @Habibkhan Sir, included (I1-I4) also into the answer.

let me know where I am doing wrong??

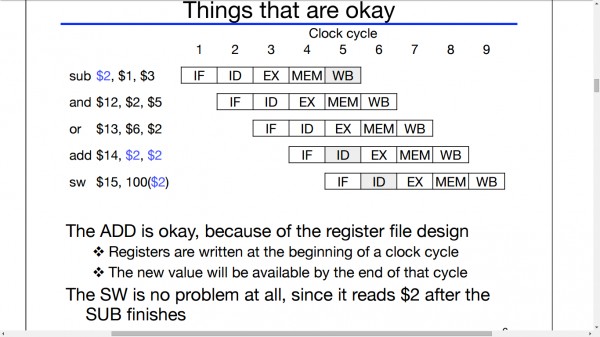

ref:-https://courses.cs.washington.edu/courses/cse378/09au/lectures/cse378au09-15.pdf

In the last line also it is written that:-

The SW is no problem at all, since it reads $2 after the SUB finishes.